![]()

Aeonsemi Timing Product Line:

New Low Jitter Family –Kronos

Quick info:

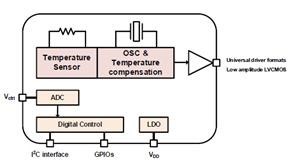

Digital & Analog compensation architecture,

for higher performance and lower power consumption

• Low power: <2mA with low-amplitude LVCMOS

• Low phase noise: -125 dBc/Hz @100Hz

• Low jitter: 52 fs

10 MHz ~ 156.25 MHz output frequency range for differential XO

• LVDS, LVPECL, HCSL, CML, Dual-LVCMOS, etc.

10 MHz ~ 76.8 MHz output frequency range for single-end LVCMOS TCXO

• Low-amplitude LVCMOS mode, 0.8V~1.2V options –

compatible with clipped sine

Temperature stability over -40 ~ 105oC operation temperature

• ± 20ppm for differential XO options

• ± 0.5/0.28/0.05 ppm for TCXO options

VCXO, DCXO, VCTCXO options

Built-in power supply noise rejection

5032, 3225, 2520, 2016 industry-standard package options

Application examples: Low Jitter is key

• TCXO

• 26MHz for GPS

• 32MHz for Lora

• 19.2/38.4/38.88MHz for SyncE/1588 in small cell & networking switch

• 10MHz in Test equipment

• XO

• Traditional Networking

• 100MHz for PCIe 4,5,6 Clock

• 156.25MHz for SERDES Clock

• 148.5MHz for Pro Video

Aeonsemi range:

More about Link Nordic frequency products

For technical support and prices, please contact our Product Sales Manager :